Проектирование модуля оперативного запоминающего устройства

Содержание

Введение

1. Проектирование

ОЗУ

.1

Исходные данные

1.2

Расчет накопителя

.3

Блок местного управления

.4

Принципиальная схема модуля ОЗУ

.5

Временная диаграмма модуля ОЗУ

.

Проектирование узлов процессора

.1

Структурная схема АЛУ

.2

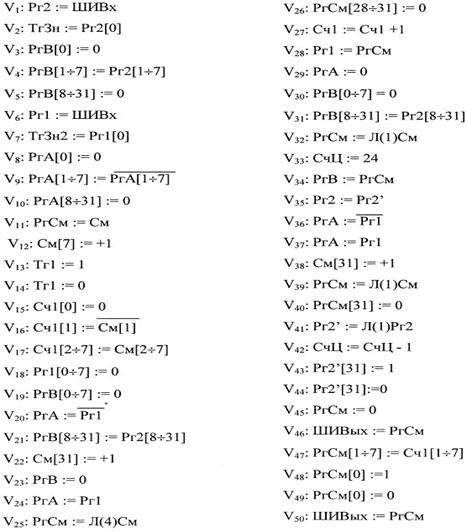

Формализованная граф-схема алгоритма

.3

Логическое проектирование управляющего устройства для АЛУ

Заключение

Литература

Введение

Наше время называют временем компьютерной

революции. Создание технологических процессов, которые позволили на одном срезе

кристалла площадью в несколько десятков квадратных миллиметров размещать

электронные схемы, состоящие из десятков и сотен тысяч логических активных

элементов, позволило в массовых количествах производить микропроцессоры,

которые по своим параметрам и функциональным возможностям превосходят

центральные процессоры некоторых больших дорогостоящих ЭВМ. В семейство

научно-технических направлений, составляющих содержание информатики, входят

теория и практика, связанные с созданием ЭВМ как технического устройства.

Цели курсового проектирования по дисциплине

“Проектирование ЭВМ, комплексов, систем”:

- освоить

методы проектирования и электрического расчета модуля оперативной памяти;

- освоить

методы проектирования АЛУ и управляющего устройства для него.

Курсовой проект состоит из следующих частей:

- проектирование,

электрический расчет и построение временных диаграмм модуля ОЗУ;

- построение

принципиальной схемы модуля ОЗУ;

- логическое

проектирование АЛУ для умножения чисел с плавающей точкой;

- логическое

проектирование узлов процессора управляющего устройства для АЛУ;

- построение

принципиальной схемы управляющего устройства.

1. Расчет статического модуля

.1 Исходные данные

Быстродействие модуля памяти- 200нс.

Разрядность-32

Объем памяти-128 Кбайт

Тип интерфейса - МПИ

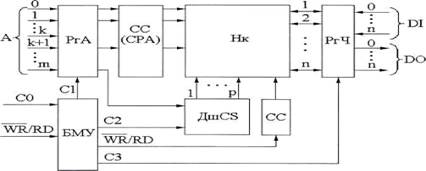

Модуль ОЗУ построен по структурной схеме,

приведённой на рисунке ниже.

Рис.1

.2 Расчет накопителя

Запоминающее устройство в соответствии со

структурной схемой состоит из накопителя, адресной части, включающей в себя

регистр адреса (РгА), схему размножения адреса (СРА), дешифратор выбора

микросхем (ДшСБ), разрядной части (регистра числа - РгЧ) и блока местного

управления (БМУ).

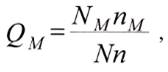

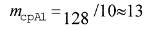

Число БИС ЗУ, используемых в накопителе модуля,

определяется независимо от способов построения накопителя :

где NM - количество чисел (адресов) в

ОЗУ; VI^ - число разрядов в ОЗУ,и n - количество чисел и разрядов в БИС ЗУ

соответственно. M=2Mм=32=64K=8

В качестве микросхемы памяти накопителя

используется БИС ЗУ типа К538РУ25, статические и динамические параметры которой

приведены в таблице 1.

Таблица 1

|

Обознач.

ИМС

|

Тип

ячейки памяти

|

Информ.

емкость, бит

|

Время

выборки адреса, нс

|

Тип

выхода

|

Напряж.

питания, В

|

Мощность

потреб. В

|

Тип

корпуса

|

|

К538РУ25

|

КМДП

|

52428

|

70

|

Три

|

5

|

0,0

|

2124.28-4

|

В качестве схем управления накопителем выберем

микросхемы серии К555 и оценим ориентировочные затраты оборудования,

необходимые для реализации модуля ОЗУ.

Накопитель, как правило, представляет собой

прямоугольную матрицу микросхем памяти, имеющую NM/N строк и пм/п

столбцов.

Общее количество микросхем в накопителе модуля

ЗУ составит

Qhk=(2048K/64K)(32/8)=128.

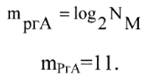

Число разрядов (триггеров) РгА находится из

выражения

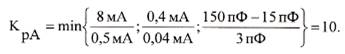

Для построения схемы размножения адреса

используем элементы К1500РУ470 - шесть инверторов в одном корпусе, имеющих

следующие параметры: I0l=8mA;

I0h=0,4mA, Cl lim = 150пФ.

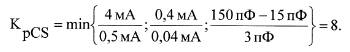

Определим значение КрA:

Число элементов в последнем ярусе СРА

так как (нагрузочной способности элементов

регистра адреса), то схема размножения состоит из одного яруса.

При этом в соответствии с

Рассчитаем дешифратор выбора микросхем (ДшС8).

Число выходов дешифратора CS S=11, а число входов ДшСБ q=6.

Находим значение KpCS:

Определяем коэффициент объединения по цепи CS накопителяобСS

=32/8=4.

Разрядная часть включает в себя регистр числа и

схемы согласования (размножения) входных данных.

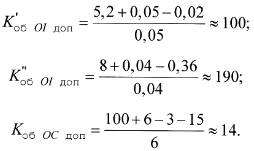

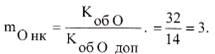

Определим коэффициент объединения по выходу:

Коб о =2048К/64К=32.

Найдём допустимый коэффициент объединения по

выходам:

Принимаем Коб 0 доп = 14. Таким

образом, -K.jMjbJb < , поэтому выходы БИС ЗУ делим на группы,

количество групп определяется следующим образом:

БИС ЗУ в группе объединяем по схеме проводного

ИЛИ, а группы между собой по схеме логического ИЛИ.

Определим коэффициент объединения по входным

информационным цепям накопителя:

Коб DI =2048К/64К=32.

.3 Блок местного управления

Блок местного управления (БМУ) предназначен для

выработки сигналов, управляющих работой регистров и накопителя, если процессор

не может обеспечить подачу этих сигналов в модуль (блок) ЗУ.

На вход БМУ поступает сигнал обращения (CS) к

данному модулю (блоку) и сигнал режима работы (запись-считывание - WR / RD).

БМУ может быть построен на различных логических элементах, например на

инверторах с применением LC-цепочек (линий задержек), или на одновибраторах,

например типа ATI, АГЗ. Если есть задающая частота синхронизации с процессора,

то БМУ можно представить в виде распределительного устройства, выполненного

различными способами. Например, в качестве БМУ возможно применение контроллеров

синхронизации типа КР583ВГ1. Потребность в оборудовании для выработки сигнала

WR/RD равно потребности в оборудовании для одного из адресных сигналов.

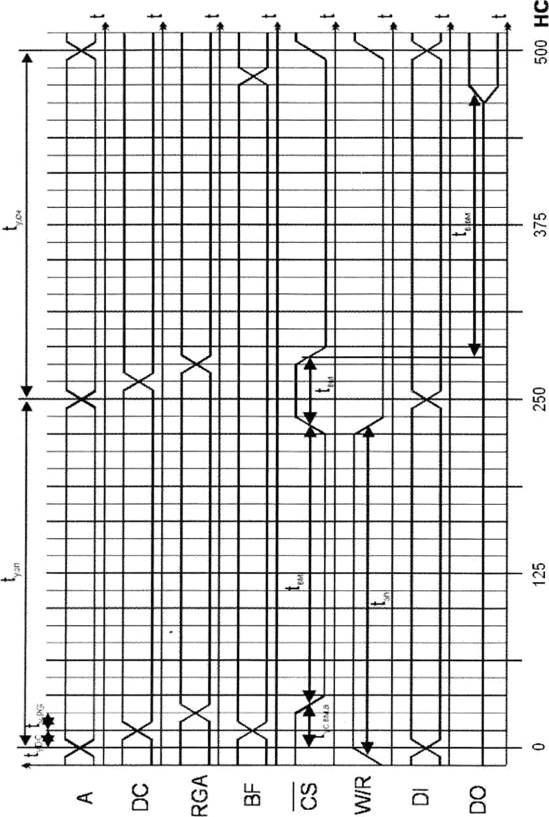

Временные диаграммы МС статического ОЗУ

приведены на рисунке и на плакате. В режиме записи к МС сначала подводят сигнал

кода адреса А, сигнал записи W/R = 1 и информационный сигнал D (на вход DI).

Затем устанавливают сигнал CS с задержкой tyC BM.a (время

установления адреса). На рисунке обозначено:

τвм

- длительность сигнала CS;

τвм

- длительность паузы в последовательности сигналов CS, которую следует

выдержать для восстановления потенциалов емкостных элементов схемы; tcx.a.вм.

- время сохранения адреса после снятия сигнала CS. В течение цикла записи выход

МС DO находится в высокоумном (третьем) состоянии.

В цикле считывания порядок подачи сигналов тот

же, что и при записи но при W/R = 0.

Время появления сигнала на информационным выходе

DO определяют параметрами:

- tв.вм.

- время выбора данных;

- tв.a.

- время выбора адреса, причем

в.a.

= tв.вм. + tус.вм.а.

Допустимые пределы значений временных параметров

МС указывают в таблицах.

Таблица 2 Таблица обозначения сигналов.

|

Наименование

сигнала

|

Обозначение

|

|

международное

|

|

Адрес

|

А

|

|

Выбор

МС

|

CS

|

|

Запись

|

WR

|

|

Считывание

|

RD

|

|

Запись/считывание

|

W/R

|

|

Входные

данные

|

DI

|

|

Выходные

данные

|

DO

|

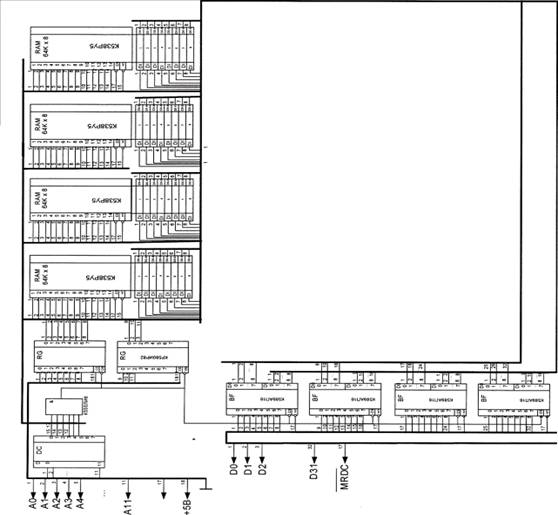

.4 Принципиальная схема модуля ОЗУ

Рис. - Принципиальная схема ОЗУ

1.5 Временная диаграмма модуля ОЗУ

Рис.- Временная диаграмма модуля ОЗУ.

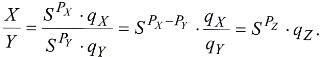

2. АЛУ для деления чисел с фиксированной точкой

Деление в ЭВМ обычно сводится к

последовательности вычитаний делителя сначала из делимого, а затем из образующихся

в процессе деления частичных остатков и сдвига последних. Алгоритмы деления

аналогичны алгоритму деления при ручном счёте. Рассмотрим особенности деления

на примере целых чисел. Пусть

= X/Y,

где X - делимое, представляемое обычно двойным

словом с 2п-1 цифровых разрядов, Y - делитель и Z - частное, представленные

одинарными словами с п-1 цифровых разрядов. Для простоты будем использовать

целые числа, представленные в прямом коде.

Чтобы разместить Z в п-1 цифровых разрядах,

необходимо выполнить условие | Z | < 2n-1. Это возможно при (| X'

| - | Y | ) < 0, где | X' | = 2-(n-1) | X |. Для получения | X' |

- | Y | следует вычесть из делимого делитель | Y | , выровняв их так, чтобы

младший разряд | Y | был под n-м разрядом | X |. Этого можно достичь, сдвинув |

Y | относительно | X | на n-1 разряд влево.

Если результат пробного вычитания больше нуля,

то | Z | > 2n-1 и деление невозможно, если он меньше нуля, то

можно выполнить деление.

Деление выполняется в соответствии с формулой

Если делимое равно 0, то результат принимается

равным 0 без деления. Если при вычитании порядков образовалось переполнение с

положительным знаком или делитель равен 0, то деление не производится и

формируется сигнал прерывания.

Схема АЛУ деления с неподвижным делителем (более

подробная) изображена на рис. 1. На схеме присутствуют следующие узлы:

См - сумматор; Рг1 - входной регистр делителя;

РгА - входной регистр сумматора, в который

поступает прямой или обратный код делителя;

РгСм - выходной регистр сумматора, в котором

образуется частичный остаток; РгВ - регистр старших разрядов делимого;

Рг2 - регистр младших разрядов делимого;

Рг2' - вспомогательный регистр для сдвига

делимого;

ТгЗн1,ТгЗн2 - триггеры знаков делимого и

делителя;

СчЦ - счётчик циклов для подсчёта числа

полученных цифр частного.

.1 Структурная схема АЛУ

Рис. 1. Структурная схема АЛУ.

РгА, РгВ - регистры, используемые для передачи

на сумматор смещённых порядков делителя и делимого при получении разности

порядков и для передачи на сумматор мантиссы делителя и частичного остатка при

получении мантиссы частного;

Сч1 - счётчик, для хранения смещённого порядка

частного;

ТгЗн1, ТгЗн2 - триггеры знаков;

Тг1 - триггер переполнения порядка.

Операция начинается с приёма операндов в Рг1 и

Рг2, фиксации их знаков в триггерах знака и передачи во входные регистры

сумматора РгА и РгВ смещённых порядков операндов:

Рг2 := ШИВх, ТгЗн := Рг2[0], РгВ[0] := 0,

PrB[l÷7] := Рг2[1÷7],

РгВ[8÷31]

:=0;

Рг1 := ШИВх, ТгЗн2 := Рг1[0], РгА[0] := 0,

РгА[1÷7]

:= PrA[l+7], PrA[8+31] := 0

Затем вычисляется разность порядков X и Y ,

размещаемых в левых байтах слов: РгСм := См, См[7] :=+1;

В результате сложения прямого кода смещённого порядка

X и дополнительного кода смещённого порядка Y в левом байте См образуется

разность порядков. Для получения смещённой разности порядков к найденной

разности следует прибавить смещение (1 к разряду См[1]). Однако коррекция

выполняется другим путём. Первоначально анализируются значения См[0] и См[1].

Если это 00, то получен положительный непереполненный порядок +р. В смещённый

он преобразуется инверсией См[1]. Отсутствие переполнения фиксируется триггером

Тг1 (Тг1 := 0). Если См[0÷1] = 01, то

имеет место положительное переполнение порядка. В этом случае вырабатывается

сигнал прерывания по переполнению порядка.

Если См[0÷1]

= 11, то получен отрицательный порядок -р. Смещённый порядок образуется после

инверсии См[1] и установки См[0] := 0. Отсутствие переполнения порядка

фиксируется установкой Тг1 := 0.

Если См[0÷1]

= 10, то получено отрицательное переполнение порядка, но исчезновение порядка

не фиксируется, так как переполнение может исчезнуть при нормализации

результата. Факт переполнения фиксируется установкой Trl := 1. Для смещения

порядка инвертируется См[1].

Микропрограмма вычитания порядков и получения

смещённого порядка частного имеет вид:

если См[0÷1]

= 01 то прерывание по переполнению порядка;

если См[0÷1]

= 10 то Trl := 1 иначе Trl := 0;

Сч1[0] := 0, Сч1[ 1 ] := См[1], Сч1[2÷7]

:=Cm[2÷7];

Далее необходимо проверить, что мантисса

делимого меньше мантиссы делителя. Если это не так, делитель денормализуется на

один 16-ричный разряд влево:

Рг1[0÷7]

:= 0, РгВ[0÷7] :=0;

РгА :=Рг1, РгВ[8÷31]

:=Рг2[8÷31],

См[31] :=+1;

если См[0]≠0 то МД <метка

микропрограммы деления мантисс;

РгВ := 0, РгА := Рг1;

РгСм := Л(4)См, РгСм[28÷31]

:= 0, Сч1 :=Сч1 +1; Рг1 :=РгСм;

Затем производится деление мантисс, выполняемое

следующей микропрограммой:

МД:: РгА := 0, РгВ[0÷7]

= 0, РгВ[8÷31] := Рг2[8÷31],

РгСм := Л(1)См, СчЦ := 24;: если СчЦ = 0 то МК

<МК

- метка микрокоманды, с которой начинается

заключительная часть микропрограммы, записанная ниже>;

РгВ := РгСм, Рг2 := Рг2’;

РгА := если См[0] = 0 то Рг1 иначе Рг1;

если См[0] = 1 то См[31]:=+1,

РгСм := Л(1)См, РгСм[31] := 0, Рг2’ := Л(1)Рг2,

СчЦ := СчЦ - 1; Рг2’[31] := если См[0] = 0 то 1 иначе 0;

идти к Ml;

После завершения деления мантисс в Рг2[8÷31]

находится мантисса частного.

Затем анализируются значения Trl и Сч[0÷1]

для получения порядка результата.

В таблице 3 приведены варианты значений Trl и

Сч1[0÷1]

после вычитания порядков и соответствующие значения смещённых порядков. В этой

же таблице приведены новые значения, которые могут иметь место после

денормализации делителя или нормализации частного.

Таблица 3

|

Результат

вычитания

|

После

изменений порядка результата

|

|

Тг

|

Сч1[0÷1]

|

Рсм

|

Тг

|

Сч1

[0÷1]

|

Рем

|

|

|

|

0

|

01

|

+

Р

|

|

0

|

01

|

+Р

|

|

|

|

|

|

|

0

|

10

|

+

00

|

|

|

|

0

|

00

|

-р

|

|

0

|

00

|

+Р

|

|

|

|

|

|

|

0

|

01

|

+р

|

|

|

|

1

|

01

|

-

00

|

|

1

|

01

|

-

00

|

|

|

|

|

|

|

1

|

-р

|

В соответствии с табл.6 производится проверка

полученного порядка результата и формирование в РгСм окончательного результата:

если (Trl = 1)˄(Сч1[0÷1]

= 01) то РгСм := 0, ШИВых := РгСм; конец;

если (Тг1= 0) ˄ (Сч1[0÷1]

= 10) то прерывание по переполнению;

РгСм[1÷7]

:= Сч1[1÷7],

РгСм[0] := если ТгЗн ≠ ТгЗн2 то 1 иначе 0, ШИВых := РгСм;

конец;

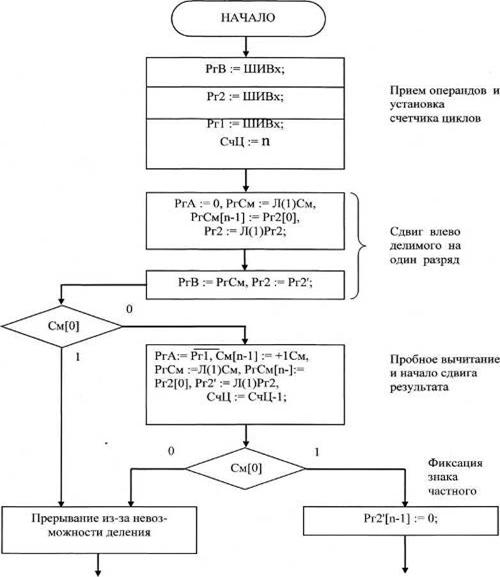

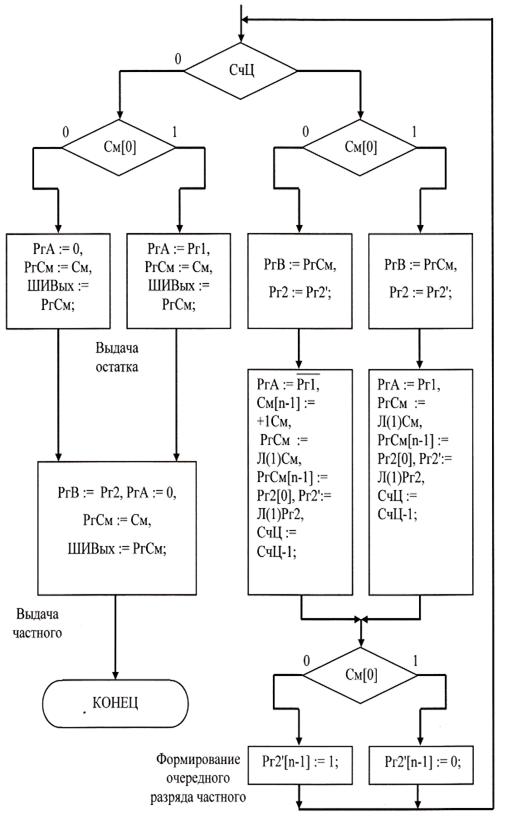

.2 Формализованная граф-схема алгоритма

Рис. 5. Формализованная граф-схема алгоритма

(ГСА)

2.3 Логическое проектирование управляющего

устройства для АЛУ

На основании имеющейся микропрограммы выполнения

операции и формализованной граф-схемы алгоритма строим граф интерпретирующего

микропрограмму автомата Мура (рис. 6). Возможно также использование автомата

Мили.

Рис.6. Граф автомата Мура.

Приняты следующие обозначения:0,Q1,Qi..,Qr

- состояния автомата, соответствующие каждой микрокоманде, входящей в

микропрограмму; г - число микрокоманд;1,U2,Ui,..,Uk

- оповещающие сигналы АЛУ (операционного блока) - знаковые разряды

регистров, выходы счётчиков, выходы формирователя признаков результата и т.д.;

Условия перехода от микрокоманды к микрокоманде

представляются в виде конъюнкции осведомительных сигналов, влияющих на переход.

Каждая конъюнкция выписывается так, чтобы набор значений осведомительных

переменных, обращающих конъюнкцию в 1, соответствовал условию перехода. При

безусловном переходе конъюнкция заменяется на константу 1,

Начальным состоянием автомата Мура - Q0

отображаются начало и конец микропрограммы. При этом предполагается, что автомат

является циклическим, т.е. допускающим многократную повторяющуюся выработку

последовательностей управляющих сигналов.

По числу состояний автомата r определяем число

элементарных автоматов (двухступенчатых триггеров), требуемых для представления

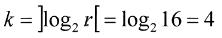

состояний автомата:

Затем поставим в соответствие наборы значений

состояний триггеров состояниям автомата (табл. 4).

Таблица 4 Таблица для программирования ПЛМ

Таблицу 4 можно также использовать для

программирования ПЛМ.

Так как четыре элемента памяти могут находиться в

шестнадцати различных состояниях, а используется все шестнадцать, то

минимизация схем не возможна.

Составление и минимизация логических выражений

для управления памятью автомата Мура на D-триггерах:

Элементы памяти - D-триггеры изменяют своё

состояние «О -» 1» при подаче сигнала «1» на основной вход v и изменяют своё

состояние «1 -> О» при подаче сигнала «О» на основной вход v. Поэтому

управляющие входные сигналы для D-триггеров можно записать сразу.

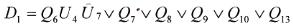

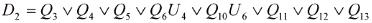

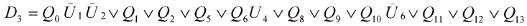

Входные управляющие сигналы первого триггера:

Входные управляющие сигналы второго триггера:

Входные управляющие сигналы третьего триггера:

Входные управляющие

сигналы Четвертого триггера:

Отметим, что для реализации логических функций в

управляющем автомате удобно использовать микросхему ПЛМ - программируемую

логическую матрицу.

Далее из 4 триггеров и дешифратора с 16 выходами

строим схему выделения состояний управляющего автомата, взяв для определённости

триггеры типа D:

оперативный память накопитель логический

Заключение

В процессе работы были сделаны действия:

. Спроектирован модуль ОЗУ быстродействием 70

(200 по заданию), с разрядностью 32 бит и объемом памяти 128 Кб.

. Спроектированы узлы процессора - АЛУ и

управляющего устройства для реализации функции деления чисел с фиксированной

точкой в шестнадцатиричной системе счисления. Составлена пояснительная записка

из 23 страниц листах формата А4.

. Подготовлен графический материал

объемом 2 листа формата А1, включающие:

принципиальную схему модуля ОЗУ;

временную диаграмму работы модуля;

функциональную схему ОЗУ;

формализованный граф микропрограммы;

принципиальную схему УУ;

Данная работа помогла лучше разобраться в

принципах работы и устройства основных устройств любого компьютера. Без знания

этих элементарных вещей, вряд ли можно надеяться на понимания принципов

устройства и работы вычислительных машин.

Литература

1. Организация ЭВМ и систем: Учебное

пособие. Ростов н/Д: РГУПС, 2000.

2. Каган Б. М. Электронные вычислительные

машины и системы: Учеб. пособие для вузов. М.: Энергоатомиздат, 1991.

3. Майоров В. Д. Проектирование ОЗУ:

Методические указания к курсовому проектированию. Ростов н/Д: РГУПС, 1997.

4. Майоров В. Д. Процессоры ЭВМ:

Методические указания к курсовому проектированию. Ростов н/Д: РГУПС, 1997.

5. Цифровые и аналоговые интегральные

микросхемы: Справочник /С.В. Якубовский и др./ - М.: Радио и связь, 1990.